ashourism

Newbie level 6

Hi,

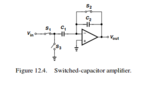

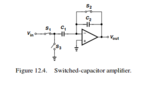

i am trying to simulate a basic ideal switched cap circuit to make a non inverting amplifier based on on analysis in Ch.12 of Razavi's : Design of Analog CMOS Integrated Circuits, ofc due to copyright i couldn't upload more than those two pictures but please if you have the book try to read the circuit description

What i understand is that when S1, S2 Closes Q(C1) = Vin*C1, then When S1,S2 Opens and S3 Closes it pushes V(C1) to zero given that feedback through C2 pushes the node between C1 and C2 to ground, and due to charge transfer and applying

Q(Total) = Vin* C1 = 0*C1 + Vout * C2 thus Vout = (C1/C2) * Vin

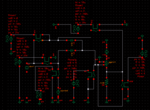

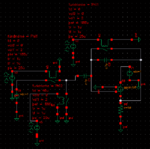

am using Cadence IC511, transient analysis however i am really unable to get any reasonable results my circuit is attached i am using ideal switches from Analog Lib

Open Voltage =0.999

Close Voltage = 1.00001

ROpen = 1TOhm

Rclose = 100uOhm

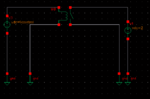

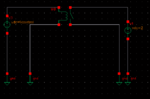

The Switch Transfer Characterstics was simulated lonely to check it first using this circuit, using a DC analysis with a sweep on Vcontrol from -3v to +3v

Switch Test Circuit:

Switch Test Circuit Output

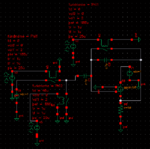

Non-Inverting Switched Capacitor Circuit, Clks are displayed on the circuit below

note : I also used an Ideal high gain OTA Model for the OpAmp using a VCCS from AnalogLib and an Rout of 1MOhm

Simulated Output of Non-Inverting Switched Capacitor Circuit :

I hope some one can help me with this

Thanks

i am trying to simulate a basic ideal switched cap circuit to make a non inverting amplifier based on on analysis in Ch.12 of Razavi's : Design of Analog CMOS Integrated Circuits, ofc due to copyright i couldn't upload more than those two pictures but please if you have the book try to read the circuit description

What i understand is that when S1, S2 Closes Q(C1) = Vin*C1, then When S1,S2 Opens and S3 Closes it pushes V(C1) to zero given that feedback through C2 pushes the node between C1 and C2 to ground, and due to charge transfer and applying

Q(Total) = Vin* C1 = 0*C1 + Vout * C2 thus Vout = (C1/C2) * Vin

am using Cadence IC511, transient analysis however i am really unable to get any reasonable results my circuit is attached i am using ideal switches from Analog Lib

Open Voltage =0.999

Close Voltage = 1.00001

ROpen = 1TOhm

Rclose = 100uOhm

The Switch Transfer Characterstics was simulated lonely to check it first using this circuit, using a DC analysis with a sweep on Vcontrol from -3v to +3v

Switch Test Circuit:

Switch Test Circuit Output

Non-Inverting Switched Capacitor Circuit, Clks are displayed on the circuit below

note : I also used an Ideal high gain OTA Model for the OpAmp using a VCCS from AnalogLib and an Rout of 1MOhm

Simulated Output of Non-Inverting Switched Capacitor Circuit :

I hope some one can help me with this

Thanks