electroM

Member level 4

- Joined

- Jul 19, 2013

- Messages

- 72

- Helped

- 11

- Reputation

- 22

- Reaction score

- 11

- Trophy points

- 18

- Location

- Pune, INDIA

- Activity points

- 384

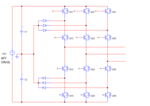

input is 48v 100Ah battery.

required output is for 1kVA transformer.

How to use diode clamped (NPC) inverter.

how to Design line capacitor?

pls help?????:?:

required output is for 1kVA transformer.

How to use diode clamped (NPC) inverter.

how to Design line capacitor?

pls help?????:?: