ruby1212

Junior Member level 3

Hello all,

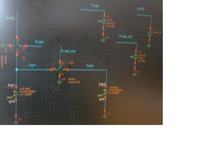

I am trying to simulate a very basic circuit but i don't know why it does not work. The goal is to generate a ramp.

Below the picture: the basic principle is to charge a small capacitor which will be "poured" step by step into a bigger one.

In my simulation i have two capacitors and i'm using an ideal switch "vswitch" from mgclib (no resistor on my schematic).

What should i verify in the circuit ? the capacitors do not charge at all. Why can a capacitor not charge if connected to VDD through an ideal switch ?

Why can a capacitor not charge if connected to VDD through an ideal switch ?

I am wainting for your answers. Please help.

Grazie !!

I am trying to simulate a very basic circuit but i don't know why it does not work. The goal is to generate a ramp.

Below the picture: the basic principle is to charge a small capacitor which will be "poured" step by step into a bigger one.

In my simulation i have two capacitors and i'm using an ideal switch "vswitch" from mgclib (no resistor on my schematic).

What should i verify in the circuit ? the capacitors do not charge at all. Why can a capacitor not charge if connected to VDD through an ideal switch ?

Why can a capacitor not charge if connected to VDD through an ideal switch ?

I am wainting for your answers. Please help.

Grazie !!