sabu31

Advanced Member level 1

Hi

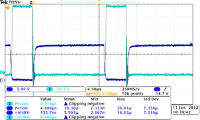

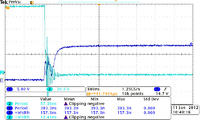

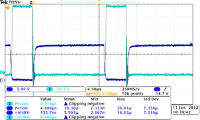

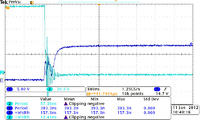

I am driving mosfets of single phase pwm inverter using ir2110, the switching frequency is 50Khz, mosfet is IRFPE50PBF. There are oscillations at turn on instant. I have attached the waveforms[drain-source, gate-source] of the lower switch of 1st leg of the inverter.Even though its not causing much of heating, i would like to eliminate it as much as possible.Please give me reason for this oscillations. Thanking you.

I am driving mosfets of single phase pwm inverter using ir2110, the switching frequency is 50Khz, mosfet is IRFPE50PBF. There are oscillations at turn on instant. I have attached the waveforms[drain-source, gate-source] of the lower switch of 1st leg of the inverter.Even though its not causing much of heating, i would like to eliminate it as much as possible.Please give me reason for this oscillations. Thanking you.