rdastyle

Newbie level 5

Error : iteration limit reached for mixed sim in ALTIUM DESIGNER

Hi everybody,

I'm working on a switch-mode power supply (" Alimentation à découpage " in French :wink .

.

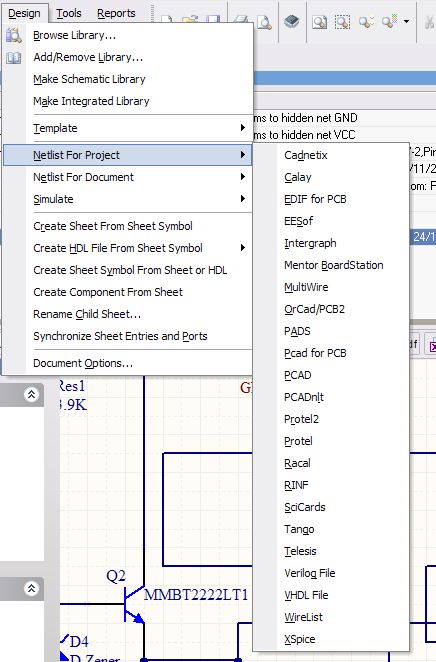

I'm using Altium Designer Summer 09 and I try to simulate it.

I've got a trouble with the element " 74AC14SC " which is a Schmitt Trigger Inverter.

Without this element, the simulation does not produce error but when using it, it does.

I attached some pictures to show the situation.

--> Have you got an idea to solve my trouble ?

Thanks.

Hi everybody,

I'm working on a switch-mode power supply (" Alimentation à découpage " in French :wink

I'm using Altium Designer Summer 09 and I try to simulate it.

I've got a trouble with the element " 74AC14SC " which is a Schmitt Trigger Inverter.

Without this element, the simulation does not produce error but when using it, it does.

I attached some pictures to show the situation.

--> Have you got an idea to solve my trouble ?

Thanks.