jerryzhao

Full Member level 3

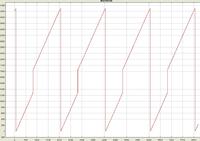

calculation of attenuation cap sar

I am testing A 16 bit SAR capcacitor ADC that design by our team. There is jump voltage when the output code cross the 1/2Vr node. I can not find the root cause of this jump voltage. Anyone meet the same result? The capacitor array is control by the thermometer code. It is singal end input of ADC(AS only care the DNL in application, in order to save die size so use the singal end input).

Detail is shown in attachment figure.

I am testing A 16 bit SAR capcacitor ADC that design by our team. There is jump voltage when the output code cross the 1/2Vr node. I can not find the root cause of this jump voltage. Anyone meet the same result? The capacitor array is control by the thermometer code. It is singal end input of ADC(AS only care the DNL in application, in order to save die size so use the singal end input).

Detail is shown in attachment figure.