magistrateee

Newbie level 1

I am making a SAR ADC and wondering if you guys can help me. I already have my SAR built and just need assistance with the others.

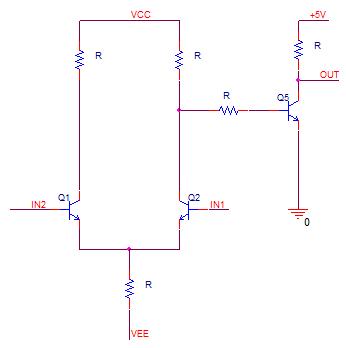

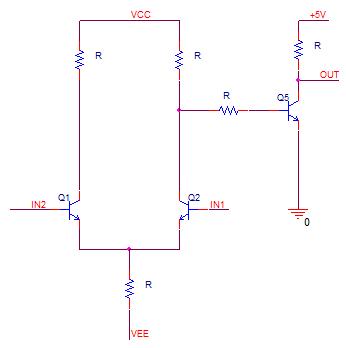

For the analog comparator I know I can use a comparator chip instead but I am trying to do it using CMOS, transistors (BJTs) or any other transistor based alternatives. The only idea I have with BJTs is using a differential amp then having it output to a switch shown below. The only problem I think is the voltage swing. I think using CMOS would be easier than using BJTs.

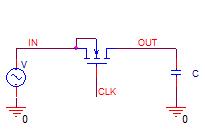

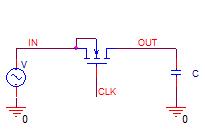

For the sample and hold can I just use an NMOS as a switch and a capacitor as shown below? What ideal size capacitor range would be best for use for this? It will be switching with a clock at a maximum of f=200Khz but I can always cut it down if necessary to get this to work.

For the DAC just like the comparator I do not plan to use a DAC chip. I am planning to use the R2R setup such as on this page: **broken link removed**. Would this exact setup be good enough? I know I can do a charged redistribution design but that would I figured the R2R is much easier.

If you guys have any schematics I can take a look at or how I can make this I would really appreciate it. Pictures would really be appreciated.

Mag

For the analog comparator I know I can use a comparator chip instead but I am trying to do it using CMOS, transistors (BJTs) or any other transistor based alternatives. The only idea I have with BJTs is using a differential amp then having it output to a switch shown below. The only problem I think is the voltage swing. I think using CMOS would be easier than using BJTs.

For the sample and hold can I just use an NMOS as a switch and a capacitor as shown below? What ideal size capacitor range would be best for use for this? It will be switching with a clock at a maximum of f=200Khz but I can always cut it down if necessary to get this to work.

For the DAC just like the comparator I do not plan to use a DAC chip. I am planning to use the R2R setup such as on this page: **broken link removed**. Would this exact setup be good enough? I know I can do a charged redistribution design but that would I figured the R2R is much easier.

If you guys have any schematics I can take a look at or how I can make this I would really appreciate it. Pictures would really be appreciated.

Mag