bhaismachine

Newbie level 4

Hello,

I have recently started using IC Compiler and Hercules tools from Synopsys. I am using them for automatic place and route of gate level netlist generated using Synopsys 90nm standard cell library. When I tried to run DRC on the GDS file created using IC Compiler I received following design rule violations. I am tried to looked up about these errors and did some reading but I think it would better if I can discuss this with someone on here.

Would anyone please help me understand meaning of these DRC violations and more important a way to fix this on IC compiler? The layout was generated automatically using script. If necessary I can upload the relevant section of my script here. Thanks!

I have recently started using IC Compiler and Hercules tools from Synopsys. I am using them for automatic place and route of gate level netlist generated using Synopsys 90nm standard cell library. When I tried to run DRC on the GDS file created using IC Compiler I received following design rule violations. I am tried to looked up about these errors and did some reading but I think it would better if I can discuss this with someone on here.

Would anyone please help me understand meaning of these DRC violations and more important a way to fix this on IC compiler? The layout was generated automatically using script. If necessary I can upload the relevant section of my script here. Thanks!

Code:

ERROR SUMMARY

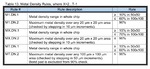

NWELL.S.1: NWELL minimum spacing between wells at same potential 0.65um

EXTERNAL nwell { } (163) ............................... 2 violations found.

PIMP.S.1: Minimum space=0.24um

EXTERNAL pimp { } (163) ................................ 2 violations found.

NIMP.S.1: Minimum space=0.24um

EXTERNAL nimp { } (163) ................................ 3 violations found.

M1.DN.1 M1 density must be < 60% in whole chip, calculated by 100umx100um step 50um

DENSITY m1 { } (163) ................................... 30 violations found.

M1.DN.2 M1 local density must be < 90% range over 20umx20um step 10um

DENSITY m1 { } (163) ................................... 899 violations found.

M2.DN.1 M2 density must be < 70% in whole chip, calculated by 100umx100um step 50um

DENSITY m2 { } (163) ................................... 36 violations found.

M2.DN.2 M2 local density must be < 90% range over 20umx20um step 10um

DENSITY m2 { } (163) ................................... 961 violations found.

M3.DN.1 M3 density must be < 70% in whole chip, calculated by 100umx100um step 50um

DENSITY m3 { } (163) ................................... 36 violations found.

M3.DN.2 M3 local density must be < 90% range over 20umx20um step 10um

DENSITY m3 { } (163) ................................... 961 violations found.

M4.DN.1 M4 density must be < 70% in whole chip, calculated by 100umx100um step 50um

DENSITY m4 { } (163) ................................... 30 violations found.

M4.DN.2 M4 local density must be < 90% range over 20umx20um step 10um

DENSITY m4 { } (163) ................................... 899 violations found.

M5.DN.1 M5 density must be < 70% in whole chip, calculated by 100umx100um step 50um

DENSITY m5 { } (163) ................................... 36 violations found.

M5.DN.2 M5 local density must be < 90% range over 20umx20um step 10um

DENSITY m5 { } (163) ................................... 961 violations found.

M6.DN.1 M6 density must be < 70% in whole chip, calculated by 100umx100um step 50um

DENSITY m6 { } (163) ................................... 36 violations found.

M6.DN.2 M6 local density must be < 90% range over 20umx20um step 10um

DENSITY m6 { } (163) ................................... 961 violations found.