Defton

Newbie level 5

HD44780 fpga core

Hi, everyone!

I need help and a lot of it.

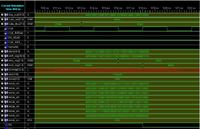

I have a project on my universty, my team needs to program the WHOLE HD44780 LCD controller in Verilog on Xilinx Spartan 3e.

We are begginers in FPGA modeling in Verilog, so it's pretty hard for us to even start. Good thing in this project is that we can use a already writing code, but we need to explain it line by line..

We found the interfacing of HD44780, but that's not the problem, we need to implement the whole core, a bit simplified. In HD44780 datasheet

https://www.sparkfun.com/datasheets/LCD/HD44780.pdf

the block diagram is not so readble, not to us. Biggest problems are CGROM, DDRAM, SEG and COM signals..

We can you use similar controller also, practicly they are all on the same basis

I googled the whole net, nothing, except interfacing, of which we have no use...

If anyone can help or if anyone has a project done it would be nice..

Greeting from Croatia, Split!

Hi, everyone!

I need help and a lot of it.

I have a project on my universty, my team needs to program the WHOLE HD44780 LCD controller in Verilog on Xilinx Spartan 3e.

We are begginers in FPGA modeling in Verilog, so it's pretty hard for us to even start. Good thing in this project is that we can use a already writing code, but we need to explain it line by line..

We found the interfacing of HD44780, but that's not the problem, we need to implement the whole core, a bit simplified. In HD44780 datasheet

https://www.sparkfun.com/datasheets/LCD/HD44780.pdf

the block diagram is not so readble, not to us. Biggest problems are CGROM, DDRAM, SEG and COM signals..

We can you use similar controller also, practicly they are all on the same basis

I googled the whole net, nothing, except interfacing, of which we have no use...

If anyone can help or if anyone has a project done it would be nice..

Greeting from Croatia, Split!