comp_engineer

Newbie level 5

hi everyone

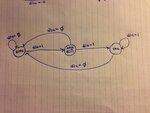

I'm writing a Moore FSM for a rising-edge detector in Verilog HDL. I have essentially written the module but I am not sure as how to transition from the "edge" state to the one state. Please look at the diagram I drew that is attached to this post. Here are my design stipulations:

and here is my Verilog code, perhaps someone can give me a few pointers

The diagram for this circuit is attached to this post. I'd really appreciate any help or assistance anyone here could provide.

I'm writing a Moore FSM for a rising-edge detector in Verilog HDL. I have essentially written the module but I am not sure as how to transition from the "edge" state to the one state. Please look at the diagram I drew that is attached to this post. Here are my design stipulations:

A rising‐edge detector is a circuit that generates a one clock‐cycle pulse every time the input signal din changes from 0 to 1.

The detector also receives the clock signal CLK and a reset signal RESET and generates the output signal pe.

Use zero as the reset state.

and here is my Verilog code, perhaps someone can give me a few pointers

Code:

`define zero 1'b0

`define one 1'b1

module MooreFSM(clk, reset, din, pe);

input clk, reset, din;

output reg pe;

reg out;

reg state;

reg next_state;

always@(posedge clk) begin

if(reset) state = 1'b0; //if there is a reset signal the state goes to state zero

else state = next_state;

end

always@(din or state) begin

case(state)

zero : //last input was a zero

begin

if(din) next_state = pe;

else next_state = 1'b0;

end

one : //we've seen 1

begin

if(din) next_state = 1'b1;

else next_state = 1'b0;

end

endcase

end

/*

always@(state) begin

case(state)

'zero: out =

'Edge: out =

'one : out =

endcase

end

*/

endmoduleThe diagram for this circuit is attached to this post. I'd really appreciate any help or assistance anyone here could provide.