ss_reddy23

Newbie level 6

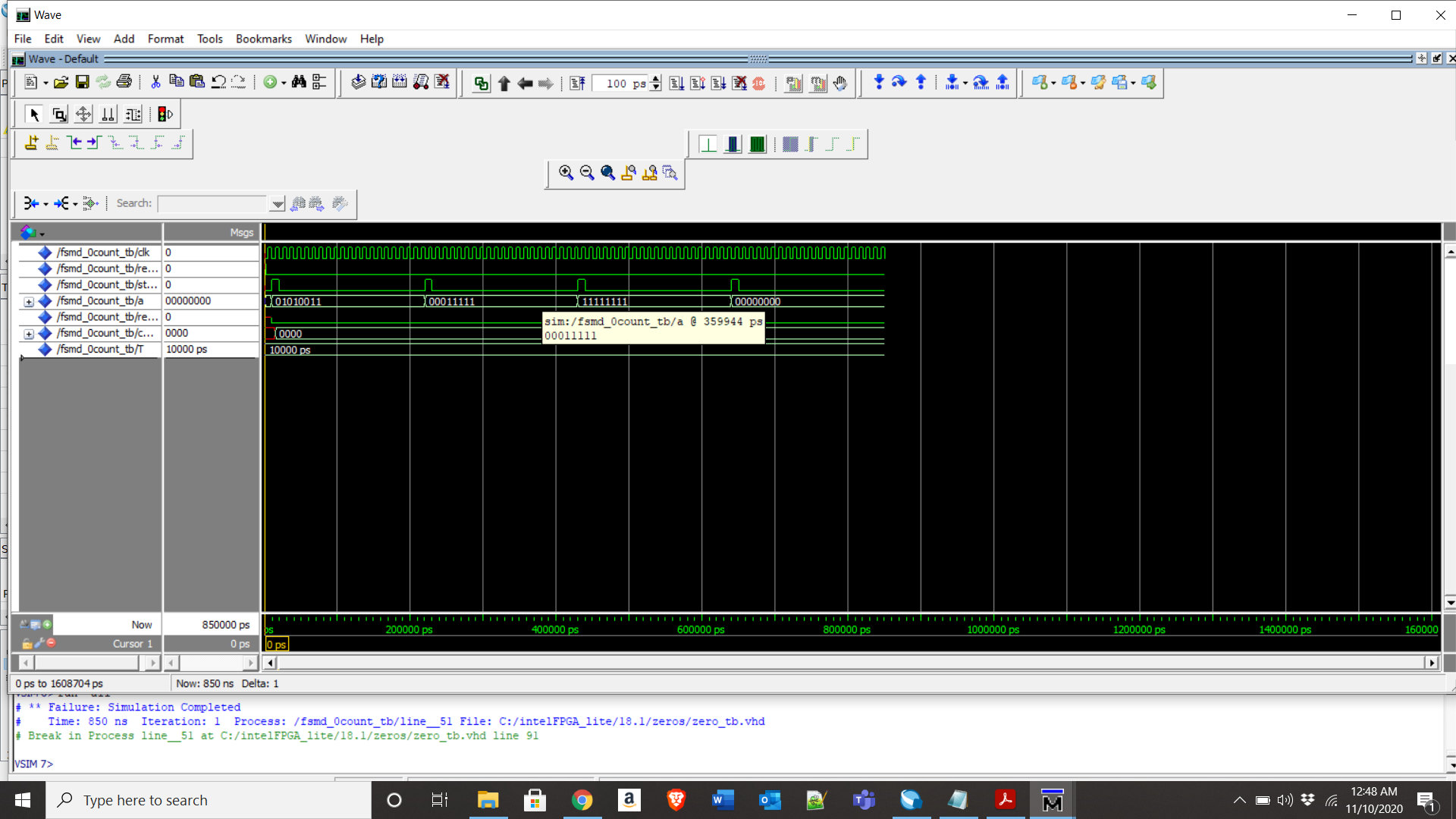

The counter does not increment and remains at zero throughout the simulation. Can you someone tell me the mistake in the code.

Functionality expected is to count number of zeros in the given input .

Functionality expected is to count number of zeros in the given input .

Code VHDL - [expand]

Last edited: