siddharthtaunk

Junior Member level 1

Hello,

Kindly help.

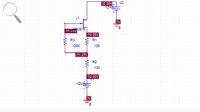

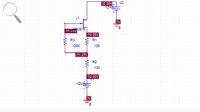

I have attached a circuit.

Please see that the gate voltage is -11V(approx).

Why is that so. I have an 100K resistor between the Gate and the point of resistor divider.

What i assume is NOTHING at the GATE pin (0V)

I have seen the same result in orcad and was perplexed.

Please help me out. Its urgent.

Thank you all in advance.

Siddharth

Kindly help.

I have attached a circuit.

Please see that the gate voltage is -11V(approx).

Why is that so. I have an 100K resistor between the Gate and the point of resistor divider.

What i assume is NOTHING at the GATE pin (0V)

I have seen the same result in orcad and was perplexed.

Please help me out. Its urgent.

Thank you all in advance.

Siddharth