coolsummer

Junior Member level 3

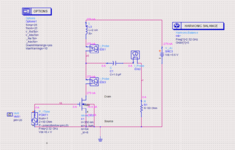

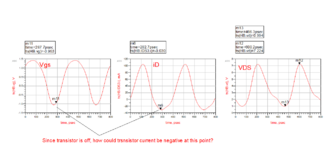

I have just simulated a simple schematic in ADS, the load ind(2nH) and cap(1pF) resonate at 2.52GHz (both of them are ideal component). The DC bias of the nmos is 0.4V, input power is 10dBm, so it is biased at class-c operation. But the simulated current of the nmos is a sine wave(even negative), other than a pulsed waveform, which is expected in class-c operation, why? Is it due to the software algorithm?(The results are the time domain waveforms after HB analysis )