d123

Advanced Member level 5

Hi,

I can never tell if I use unnecessary buffers in the circuits I work through.

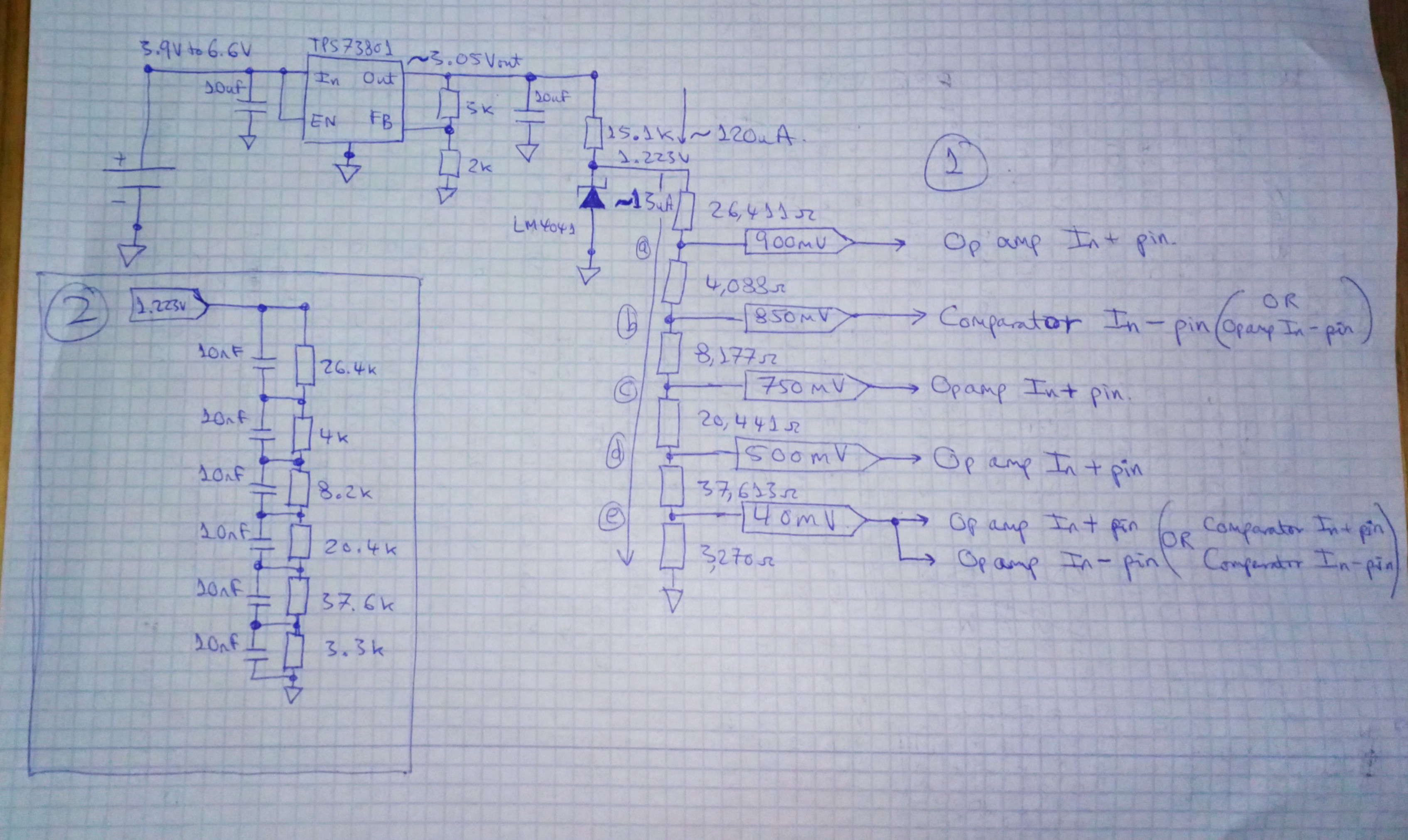

Question 1: Should buffers be used on all or any of the resistor string outputs 'a' to 'e' as they are supposed to be stable voltage references, and should two buffers be used for output 'e' as it is a reference voltage for two separate comparators (or op amps)? Or should they be perfectly fine without buffers?

Question 2: I saw this approach in an Analog Devices or Linear Technologies datasheet or app note - placing bulk capacitors around each resistor in a string to reduce noise/fluctuations in the output voltages. Is that a good approach to follow in the schematic in the picture?

Thanks.

I can never tell if I use unnecessary buffers in the circuits I work through.

Question 1: Should buffers be used on all or any of the resistor string outputs 'a' to 'e' as they are supposed to be stable voltage references, and should two buffers be used for output 'e' as it is a reference voltage for two separate comparators (or op amps)? Or should they be perfectly fine without buffers?

Question 2: I saw this approach in an Analog Devices or Linear Technologies datasheet or app note - placing bulk capacitors around each resistor in a string to reduce noise/fluctuations in the output voltages. Is that a good approach to follow in the schematic in the picture?

Thanks.