020170

Full Member level 4

- Joined

- Jan 31, 2005

- Messages

- 231

- Helped

- 3

- Reputation

- 6

- Reaction score

- 1

- Trophy points

- 1,298

- Activity points

- 2,221

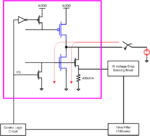

In CMOS Process, I designed Large NMOS/PMOS switch Transistor.

To protect switches from large Ids current, I designed protection circuit and inserted it.

It is supposed to operate when Ids current > 300mA , PMOS gate pull on(VDD) and NMOS gate pull down(GND). So Ids current doesnt flow any more.

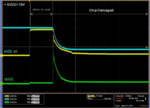

On the contrary to concerns, when large current flow through NMOS switch, switch has no damage.

Rather after large current flow, -> protection circuit operate -> NMOS gate is about to pulling down, switch has damage.

I don't understand why NMOS switch has damaged when NMOS switch is about to turn off.

In my opinion, NMOS switch damage is relevant to latch up issue.

Is there any one who help me? I want to know inside knowledge about it.

Thanks.

To protect switches from large Ids current, I designed protection circuit and inserted it.

It is supposed to operate when Ids current > 300mA , PMOS gate pull on(VDD) and NMOS gate pull down(GND). So Ids current doesnt flow any more.

On the contrary to concerns, when large current flow through NMOS switch, switch has no damage.

Rather after large current flow, -> protection circuit operate -> NMOS gate is about to pulling down, switch has damage.

I don't understand why NMOS switch has damaged when NMOS switch is about to turn off.

In my opinion, NMOS switch damage is relevant to latch up issue.

Is there any one who help me? I want to know inside knowledge about it.

Thanks.