stackprogramer

Full Member level 3

whats equation between Leff and tox in mosfet structure?

tox is width of oxide ,leff=effective length of mosfet?

whats equation(relation) between Leff and tox in mosfet structure?

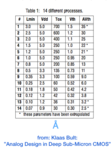

in variety technology like .5 um ,.25 um,.11 um .

please help me?

tox is width of oxide ,leff=effective length of mosfet?

whats equation(relation) between Leff and tox in mosfet structure?

in variety technology like .5 um ,.25 um,.11 um .

please help me?