tony_lth

Advanced Member level 5

Hi, Gurus,

I found one weird adjacent channel performance of the SX1268 LORA transceiver.

SX1268 datasheet as attachment "SX1268_V1.0.pdf".

The test setup as "Test_Setup1.lpg", the blue circle is the TX, and the red circle is RX board developed by us.

TX parameters: 484MHz, +10dBm, LORA SF5, PL=55, BW=500Khz,

At CH28, i.e. RX_Freq=484MHz, the RX performance is normal. As attached picture "CH28_RX.jpg", the RX level is about -30dBm.

One channel is 500KHz spacing.

But at CH24, the noise floor level is -70dBm, it should be -100dBm, so it's weird. As attachment "CH24_weird.jpg".

Only when another TX at CH24/482Mhz, and the RX signal level is more than -55dbm, then the RX CH24 performance is normal, as "CH24_normal", the noise floor level is -100dBm.

That is so weird, anyone has the solution?

Best,

Tony Liu

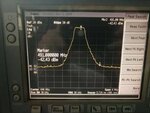

Attached "LORA_SF5_SA.jpg" is the spectrum analysis picture when TX at 490M/+17dBm. It can say that the noise floor @1MHz is -42.43dBm, if add propagation loss 30dB, the noise floor is about -70dBm. Is the aforesaid weird RX performance related to this spectrum floor?

I found one weird adjacent channel performance of the SX1268 LORA transceiver.

SX1268 datasheet as attachment "SX1268_V1.0.pdf".

The test setup as "Test_Setup1.lpg", the blue circle is the TX, and the red circle is RX board developed by us.

TX parameters: 484MHz, +10dBm, LORA SF5, PL=55, BW=500Khz,

At CH28, i.e. RX_Freq=484MHz, the RX performance is normal. As attached picture "CH28_RX.jpg", the RX level is about -30dBm.

One channel is 500KHz spacing.

But at CH24, the noise floor level is -70dBm, it should be -100dBm, so it's weird. As attachment "CH24_weird.jpg".

Only when another TX at CH24/482Mhz, and the RX signal level is more than -55dbm, then the RX CH24 performance is normal, as "CH24_normal", the noise floor level is -100dBm.

That is so weird, anyone has the solution?

Best,

Tony Liu

--- Updated ---

Attached "LORA_SF5_SA.jpg" is the spectrum analysis picture when TX at 490M/+17dBm. It can say that the noise floor @1MHz is -42.43dBm, if add propagation loss 30dB, the noise floor is about -70dBm. Is the aforesaid weird RX performance related to this spectrum floor?

Attachments

Last edited: