T

treez

Guest

Hello,

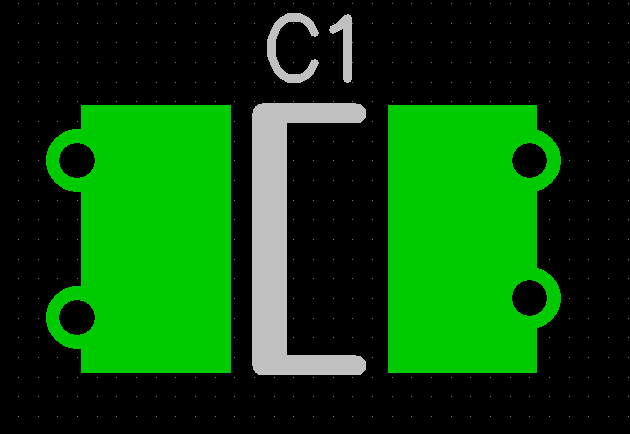

Is it acceptable to put vias in the pads of 1812 capacitors to get the current down to the bottom layer?....there is not enough room for enough vias outside of the pads as the board is so small.

Is it acceptable to put vias in the pads of 1812 capacitors to get the current down to the bottom layer?....there is not enough room for enough vias outside of the pads as the board is so small.