catalin560

Junior Member level 2

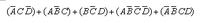

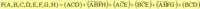

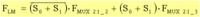

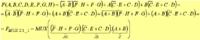

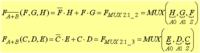

Hello! So I have the next assignment: write a verilog code for a combinational circuit that have the next values:

can this be done with a 3:1 mux with two selections?

Code:

input output

0-0-0 > 0

0-0-1 > 1

0-1-0 > 1

0-1-1 > 0

1-0-0 > 1

1-0-1 > 0

1-1-0 > 0

1-1-1 > 1can this be done with a 3:1 mux with two selections?