lifusu

Newbie level 5

hi guys!

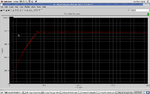

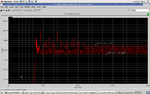

i design a pll (verilogA), 12MHz input , C2=400p, C1=40p, R2=3.3k,bandwidth=600k,Kvco=600MHz/v,Icp=20uA,when locked , the wave of Vctrl is as follows, why the Vctrl like this? i don't think it is ripple.

But when i delete divider, this condition will not occur, but the divider is ideal , why?

thx in advance!

i design a pll (verilogA), 12MHz input , C2=400p, C1=40p, R2=3.3k,bandwidth=600k,Kvco=600MHz/v,Icp=20uA,when locked , the wave of Vctrl is as follows, why the Vctrl like this? i don't think it is ripple.

But when i delete divider, this condition will not occur, but the divider is ideal , why?

thx in advance!

Last edited: