f_t

Member level 4

Friends,

I want to design a PA by Load Pull analysis in ADS at 2.95 GHz. According to its examples and the ADS's cookbook I did it, but there are some problems.

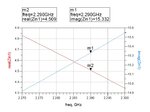

According to load pull in ADS (the below figure) if I adjust zin=250+j*1360 and zload=4.5-j15.32 I wil get PAE 64% and Pload= 44dBm.

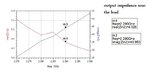

I designed the input and output matching networks with the above characteristics (below figures).

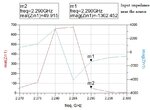

As you see at 2.95 GHz the matching networks work well. After I did simulation to see PAE and Pload, the results are so different to Pload=44dBm and PAE=64% (PAE=1.5% and Pload=-50dBm). I took a look on input matching (near the source not transistor) and output matching (near the load not transistor) they are not 50 Ohm at all! It means if I connect zload=4.5-j15.32 to output matching network, I will have 50 Ohm at output of the matching network, but if I connect the output of the transistor to the matching network I will not have 50 Ohm. The same problem is for the input matching too. You can see their behaviour below:

What is the problem? why cannot I get the PAE and Pload calculated by load pull analysis? Why are input and output matching networks not matched to 50 Ohm?

I want to design a PA by Load Pull analysis in ADS at 2.95 GHz. According to its examples and the ADS's cookbook I did it, but there are some problems.

According to load pull in ADS (the below figure) if I adjust zin=250+j*1360 and zload=4.5-j15.32 I wil get PAE 64% and Pload= 44dBm.

I designed the input and output matching networks with the above characteristics (below figures).

As you see at 2.95 GHz the matching networks work well. After I did simulation to see PAE and Pload, the results are so different to Pload=44dBm and PAE=64% (PAE=1.5% and Pload=-50dBm). I took a look on input matching (near the source not transistor) and output matching (near the load not transistor) they are not 50 Ohm at all! It means if I connect zload=4.5-j15.32 to output matching network, I will have 50 Ohm at output of the matching network, but if I connect the output of the transistor to the matching network I will not have 50 Ohm. The same problem is for the input matching too. You can see their behaviour below:

What is the problem? why cannot I get the PAE and Pload calculated by load pull analysis? Why are input and output matching networks not matched to 50 Ohm?

Last edited: