afz23

Full Member level 3

- Joined

- Nov 30, 2007

- Messages

- 183

- Helped

- 15

- Reputation

- 30

- Reaction score

- 14

- Trophy points

- 1,298

- Location

- Bangalore

- Activity points

- 2,758

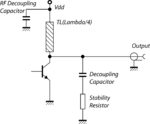

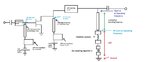

I used CFY25 Infeneon device to design(simulation) an amplifier at 12 GHz and achieved 8dB gain

and acceptable return losses in design bandwidth.

But there is a problem!!! the design shows instabilities K<1,near 4.5GHz and 7GHz.

I tried to stablize the design ,using shunt and series stablizing resistors at output and input

side,but didn't succeeded,as these stablizing circuits are eating up all the gain at 12 GHz.

Seasoned designers say,not to worry about these instabilities,go ahead and fabricate as

practically amplifier will not see those loads which is leading to oscillations,as this impedance lies

at the edge of the smith chart in right hand side(high impedance area).

Experts please comment on this!!!!

and acceptable return losses in design bandwidth.

But there is a problem!!! the design shows instabilities K<1,near 4.5GHz and 7GHz.

I tried to stablize the design ,using shunt and series stablizing resistors at output and input

side,but didn't succeeded,as these stablizing circuits are eating up all the gain at 12 GHz.

Seasoned designers say,not to worry about these instabilities,go ahead and fabricate as

practically amplifier will not see those loads which is leading to oscillations,as this impedance lies

at the edge of the smith chart in right hand side(high impedance area).

Experts please comment on this!!!!