PA3040

Advanced Member level 3

Dear All,

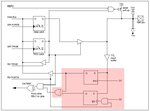

Please see the attached picture for me

This is the understanding purpose of all parts of the PORTD block diagram

I would like to understand step by step than all together at once

Therefore the attached picture have two D flip flop ,both are smiler to each other, Am I correct?

The D flip-flop tracks the input, making transitions with match those of the input D. The D stands for "data"; this flip-flop stores the value that is on the data line. It can be thought of as a basic memory cell

Let say I want to configure PortD pin 0 as an out put

Then

first bannksel

BCF TRISD,0

It would be much appreciated if some one can teach me the data flow using attached picture

Thanks in advance

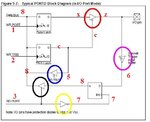

Please see the attached picture for me

This is the understanding purpose of all parts of the PORTD block diagram

I would like to understand step by step than all together at once

Therefore the attached picture have two D flip flop ,both are smiler to each other, Am I correct?

The D flip-flop tracks the input, making transitions with match those of the input D. The D stands for "data"; this flip-flop stores the value that is on the data line. It can be thought of as a basic memory cell

Let say I want to configure PortD pin 0 as an out put

Then

first bannksel

BCF TRISD,0

It would be much appreciated if some one can teach me the data flow using attached picture

Thanks in advance

Last edited: