sraheja

Newbie level 4

- Joined

- Jun 19, 2010

- Messages

- 6

- Helped

- 0

- Reputation

- 0

- Reaction score

- 0

- Trophy points

- 1,281

- Location

- Kanpur, India

- Activity points

- 1,350

I am trying simulate a modified sine wave inverter (12V to 220 V output/ 200 Watts output) based on push pull topoplogy using TL494 in LTSpice. The TL494 oscillator is being driven for a 50Hz push pull frequency.

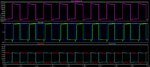

In order to create a three level voltage output, I am trying to use the dead time control feature of TL494. This has been set using resistors R14 and R15 in the attached circuit. While the output from TL494 looks OK (the dead time is clearly seen in the waveform for the totem pole output driving the mosfet gates), the voltage wave forms at the primary and secondary of the push pull transformer are not showing zero output voltage during the dead time. The voltages directly swing from -240V to +240 V, without staying at 0V level. Is it wrong to expect that during the dead time when both mosfets are off, the voltage output at the transformer secondary should also come to zero.

If however I significantly increase the load, say by reducing the load resistor R17 from 200E to 2E, I do get a modified sine wave out put but with much lower voltages (may be due to resistive voltage drops). Can some one please comment as to what might be happening in the simulation and whether the same would also be expected in the real circuit?

thanks in advance,

In order to create a three level voltage output, I am trying to use the dead time control feature of TL494. This has been set using resistors R14 and R15 in the attached circuit. While the output from TL494 looks OK (the dead time is clearly seen in the waveform for the totem pole output driving the mosfet gates), the voltage wave forms at the primary and secondary of the push pull transformer are not showing zero output voltage during the dead time. The voltages directly swing from -240V to +240 V, without staying at 0V level. Is it wrong to expect that during the dead time when both mosfets are off, the voltage output at the transformer secondary should also come to zero.

If however I significantly increase the load, say by reducing the load resistor R17 from 200E to 2E, I do get a modified sine wave out put but with much lower voltages (may be due to resistive voltage drops). Can some one please comment as to what might be happening in the simulation and whether the same would also be expected in the real circuit?

thanks in advance,