mohamed mahmoud

Junior Member level 1

- Joined

- Jan 31, 2014

- Messages

- 16

- Helped

- 0

- Reputation

- 0

- Reaction score

- 0

- Trophy points

- 1

- Activity points

- 118

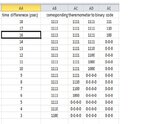

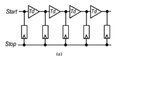

i,am working in designing time to digital converter . i need to know truth table for thermometer to binary encoder (31 to 5 bit) ??

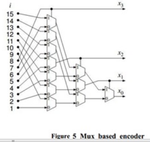

i will use mux based thermometer to binary encoder.

i will use mux based thermometer to binary encoder.