jayeffe

Junior Member level 2

Hello everyone. I apologize in advance because I don't speak English well but I try to make myself understood. I am carrying out an educational project which consists in the use of the ADDA card.

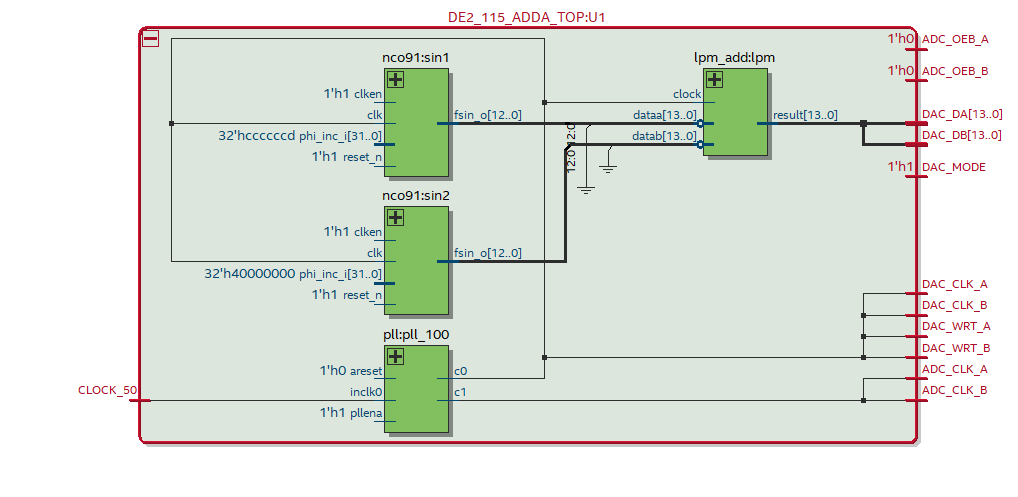

In practice, the starting point that has been suggested to me is the use of the "ADA demostration". Here the oscillator waveform is generated, summed.

In addition to this I have to create a loop that connects the digital output to the input of the dac.

Then I have to filter through fir filter.

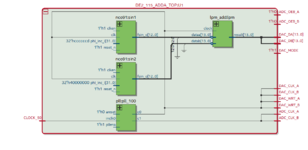

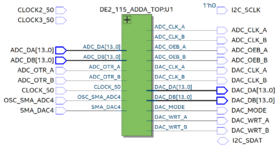

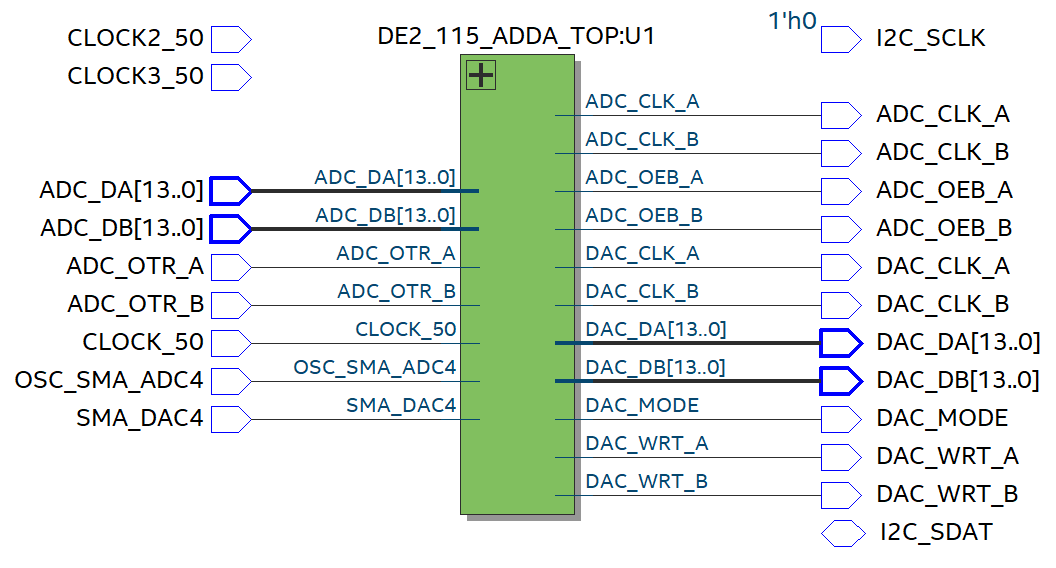

I have attached the netlist of the example project.

For filtering, I read from the internet that it is placed by taking the ADC_DA signal as input

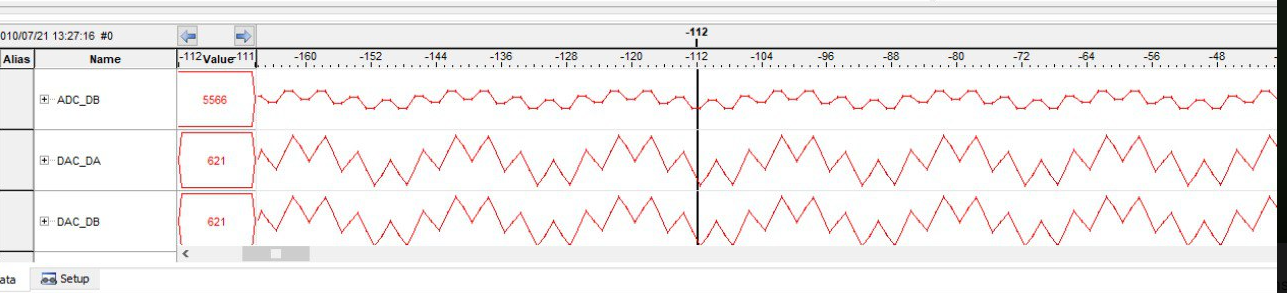

The problem I'm having with quartus is to use the signal tap.

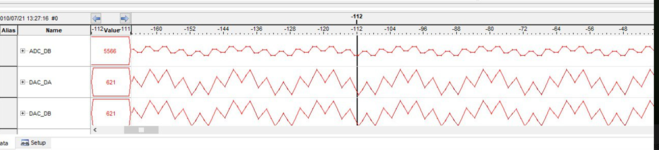

in the photo there are the signals that are part of the example project. If I add other signals, which are part of the project (for example ADC_DA) the signal tap tells me to recompile or gives me other errors.

thanks everyone for the help

In practice, the starting point that has been suggested to me is the use of the "ADA demostration". Here the oscillator waveform is generated, summed.

In addition to this I have to create a loop that connects the digital output to the input of the dac.

Then I have to filter through fir filter.

I have attached the netlist of the example project.

For filtering, I read from the internet that it is placed by taking the ADC_DA signal as input

The problem I'm having with quartus is to use the signal tap.

in the photo there are the signals that are part of the example project. If I add other signals, which are part of the project (for example ADC_DA) the signal tap tells me to recompile or gives me other errors.

thanks everyone for the help