monahanz

Junior Member level 1

- Joined

- Nov 11, 2013

- Messages

- 19

- Helped

- 0

- Reputation

- 0

- Reaction score

- 0

- Trophy points

- 1,281

- Location

- San Ramon CA

- Activity points

- 1,490

Could somebody help me on this what I'm sure is a trivial PALASM question.

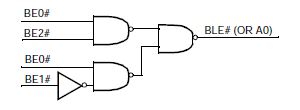

Starting with this schematic:-

There are 3 NAND gates and one Inverter (input BE1*)

I want to burn a GAL using the four inputs to get the A0 output with PALASM

Since PALSAM does not accept brackets in its EQUATIONS how do I combine the two inputs to the right hand side NAND.

I know I could make two intermediate pins and do this:-

X = \BE0 * \BE2

Y = \BE0 * BE1

/A0 = X * Y

But this uses up two (useless) pins. I considered

A0 = \BE0 * \BE2

+ \BE0 * BE1

But that does not give the correct state

Starting with this schematic:-

There are 3 NAND gates and one Inverter (input BE1*)

I want to burn a GAL using the four inputs to get the A0 output with PALASM

Since PALSAM does not accept brackets in its EQUATIONS how do I combine the two inputs to the right hand side NAND.

I know I could make two intermediate pins and do this:-

X = \BE0 * \BE2

Y = \BE0 * BE1

/A0 = X * Y

But this uses up two (useless) pins. I considered

A0 = \BE0 * \BE2

+ \BE0 * BE1

But that does not give the correct state

Last edited by a moderator: