greenjuice

Member level 1

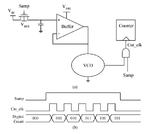

Actually i make ADC as attached image.

But i have some problem.

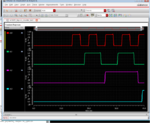

Period of VCO I designed is 0.3ns - 0.275ns at 0 - 1V input voltage.

But 12bit counter circuit I designed doesn't work below 3ns period. So they don't match.

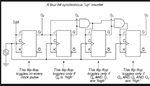

I designed synchronous counter circuit using this.(I attach synchronous counter circuit I used)

Is it possible to design the synchronous counter circuit on similar performance of my VCO?

I think it is impossible in that if the clock cycle become shorter, it is difficult for each jk flip-

flop in counter to toggle at a proper time by its transition delay time.

What do you think? please help me.

But i have some problem.

Period of VCO I designed is 0.3ns - 0.275ns at 0 - 1V input voltage.

But 12bit counter circuit I designed doesn't work below 3ns period. So they don't match.

I designed synchronous counter circuit using this.(I attach synchronous counter circuit I used)

Is it possible to design the synchronous counter circuit on similar performance of my VCO?

I think it is impossible in that if the clock cycle become shorter, it is difficult for each jk flip-

flop in counter to toggle at a proper time by its transition delay time.

What do you think? please help me.

Attachments

Last edited: