The_Babatian

Junior Member level 2

- Joined

- Feb 22, 2013

- Messages

- 22

- Helped

- 0

- Reputation

- 0

- Reaction score

- 0

- Trophy points

- 1,281

- Activity points

- 1,483

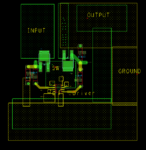

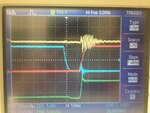

Attached is a waveform for a synchronous buck converter which, as you can see, has ringing in the output voltage (Yellow trace, AC coupled) during switching. The top two traces are gate signals, blue for low gate signal while the red for high gate signal, the bottom trace is the switching node signal. The gate driver IC I am using is LM5101 from TI and the MOSFET is BUK6218-40C,118 from NXP, I did follow the layout considerations given in the datasheet and referred to additional documents regarding how to optimize the PCB layout and placement of the DC-DC converter. Also, the dead-time between these two gate signals are programmed to be around 100ns which I think is quite sufficient, but somehow I still got this ringing issue. Can anyone help me out? thanks in advance!

Last edited: