geozog86

Member level 3

Hello!

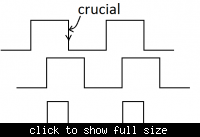

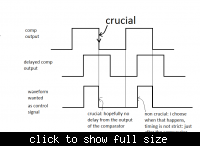

I am having an nmos switch, that i want it to shut off when my comparator gives "0". But i want it to keep on NOT conducting a bit more than the output of the comparator. So as you see in the attached pic, my idea is to delay the output of the comparator, and with an AND function to get a signal that gets 0 in the crucial moment, and stays there a bit longer....

QUESTIONS:

1-is there any other idea on how to keep the "0"=not conducting phase a bit longer?

2-(MORE IMPORTANT) can i implement somehow this function of an AND gate without the gate? so i don't have the delay of the gate? A more "hardware" solution? Something like a node where i could give my two signals (ouput and delayed version) and the AND function is inherited and happens instanteously?

Ok, it might be wishful thinking that something like that exists, but thank you in advance

PS happy easter to everyone honouring the day today

I am having an nmos switch, that i want it to shut off when my comparator gives "0". But i want it to keep on NOT conducting a bit more than the output of the comparator. So as you see in the attached pic, my idea is to delay the output of the comparator, and with an AND function to get a signal that gets 0 in the crucial moment, and stays there a bit longer....

QUESTIONS:

1-is there any other idea on how to keep the "0"=not conducting phase a bit longer?

2-(MORE IMPORTANT) can i implement somehow this function of an AND gate without the gate? so i don't have the delay of the gate? A more "hardware" solution? Something like a node where i could give my two signals (ouput and delayed version) and the AND function is inherited and happens instanteously?

Ok, it might be wishful thinking that something like that exists, but thank you in advance

PS happy easter to everyone honouring the day today