jianjing526

Member level 2

hi all,

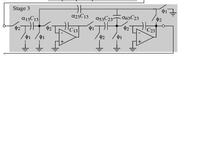

I'm designing a five-order chebyshev LPF. Three subckts cascaded to compose the filter, a one-order one and two biquads. There are five operational amplifiers. How to give out the specifications of these opamps? I'm confusing all these days!

I'm designing a five-order chebyshev LPF. Three subckts cascaded to compose the filter, a one-order one and two biquads. There are five operational amplifiers. How to give out the specifications of these opamps? I'm confusing all these days!