Junus2012

Advanced Member level 5

Dear friends,

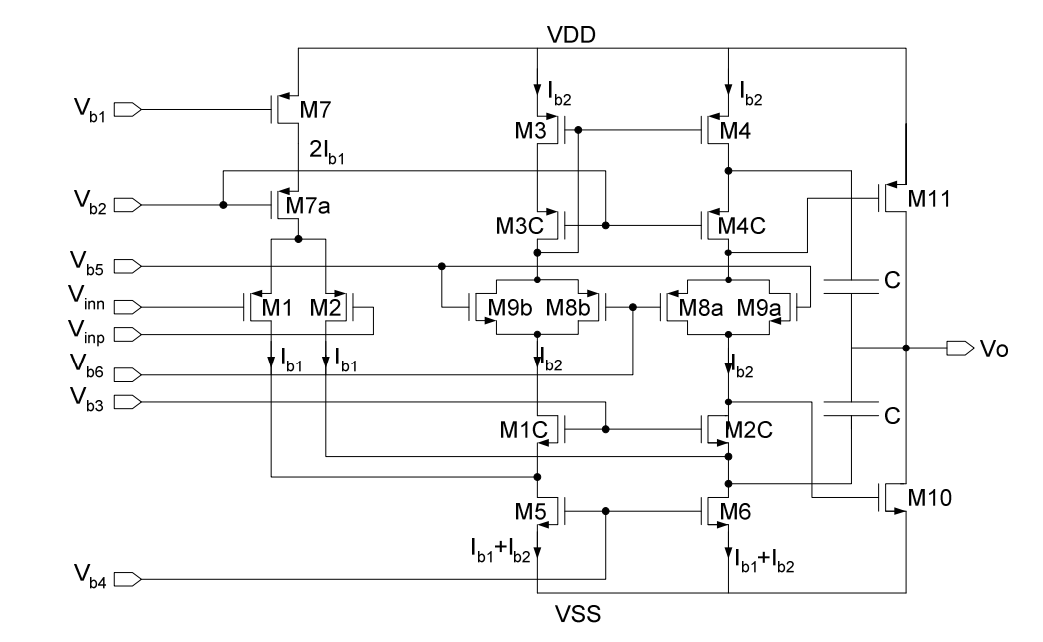

I mostly use the class AB circuit shown below for most of my design, it is like butter and bread for me, but since now I am targetting a GBW = 250 MHz, I am finding difficulty to get this value from this circuit. I cant ignore the fact the buffered op-amp is limited in speed due to the compensation capacitor so I am trying to increase the differential biasing current, increasing the output current (M11 & M10) to push away the non-dominant pole that helps in reducing CC, I killed myself to reach GBW = 100 MB with PM = 55.

I like the circuits based on folded-cascode core because it is easy to implement rail to rail input stage.

So I am not sure if there is a better buffer circuit to use ? or another possibility to extend the GBW of this circuit.

I am using the 0.35 µm technology.

The intended application is for active LPF design.

Thank you

I mostly use the class AB circuit shown below for most of my design, it is like butter and bread for me, but since now I am targetting a GBW = 250 MHz, I am finding difficulty to get this value from this circuit. I cant ignore the fact the buffered op-amp is limited in speed due to the compensation capacitor so I am trying to increase the differential biasing current, increasing the output current (M11 & M10) to push away the non-dominant pole that helps in reducing CC, I killed myself to reach GBW = 100 MB with PM = 55.

I like the circuits based on folded-cascode core because it is easy to implement rail to rail input stage.

So I am not sure if there is a better buffer circuit to use ? or another possibility to extend the GBW of this circuit.

I am using the 0.35 µm technology.

The intended application is for active LPF design.

Thank you