Alvaro Camacho Mora

Newbie level 4

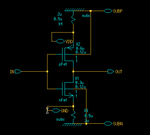

Hello! I need help I'm new in 0.13 um process using ibm8rf kit. In my first circuit and layout, I made a logic inverter. However this inverter working successfully in the schematic, but in the layout I have a big problems because the subtract mask don't connect with the transistor and I don't know if this form of connection is correct. In the adjust file, I show an image of my schematic. I use mentor graphics.

Thanks.

Thanks.