IntuitiveAnalog

Member level 2

- Joined

- May 18, 2014

- Messages

- 52

- Helped

- 1

- Reputation

- 2

- Reaction score

- 1

- Trophy points

- 1,288

- Activity points

- 1,684

Hi All,

I am designing a two stage miller opamp (pmos input differential pair) in subthreshold region. I am using 32nm technology node. The parameters are given below:

1. Supply voltage = 1V

2. Bias Current = 200nA

3. Transistor Length = 160nm=(5 Lmin)

There are no specific requirements but I have to just reduce power dissipation.

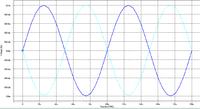

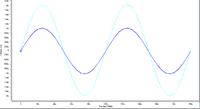

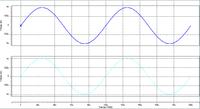

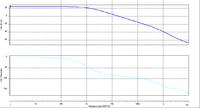

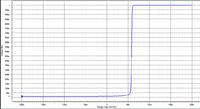

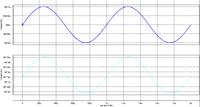

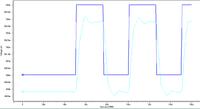

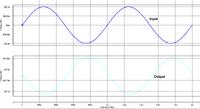

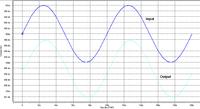

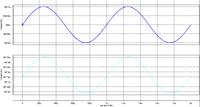

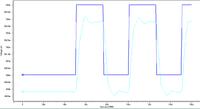

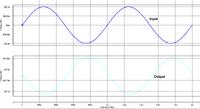

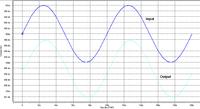

I am getting all the responses quite correct but in transient analysis the output dc level is not the same as input dc level.

I will be very much thankful if anyone could figure out how to make input and output dc level same.

Thanks

I am designing a two stage miller opamp (pmos input differential pair) in subthreshold region. I am using 32nm technology node. The parameters are given below:

1. Supply voltage = 1V

2. Bias Current = 200nA

3. Transistor Length = 160nm=(5 Lmin)

There are no specific requirements but I have to just reduce power dissipation.

I am getting all the responses quite correct but in transient analysis the output dc level is not the same as input dc level.

I will be very much thankful if anyone could figure out how to make input and output dc level same.

Thanks