ge

Full Member level 5

- Joined

- Jun 23, 2006

- Messages

- 250

- Helped

- 29

- Reputation

- 58

- Reaction score

- 29

- Trophy points

- 1,308

- Location

- Pennsylvania, USA

- Activity points

- 2,772

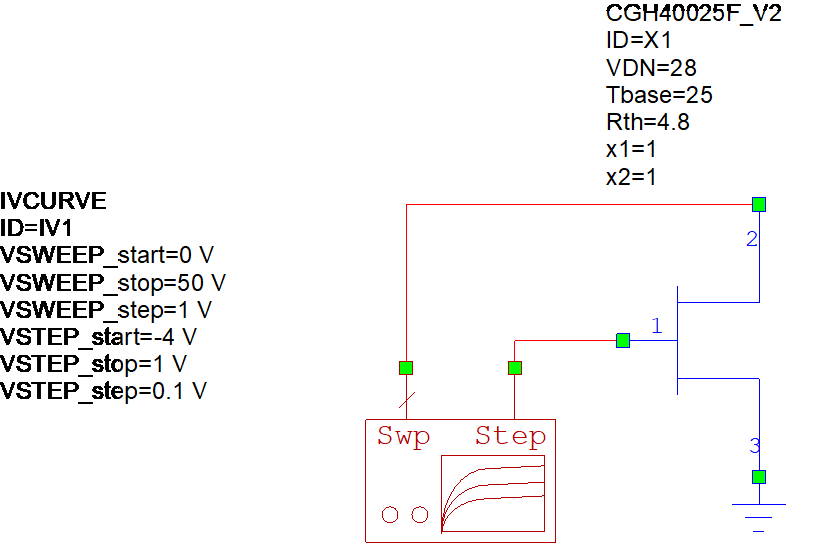

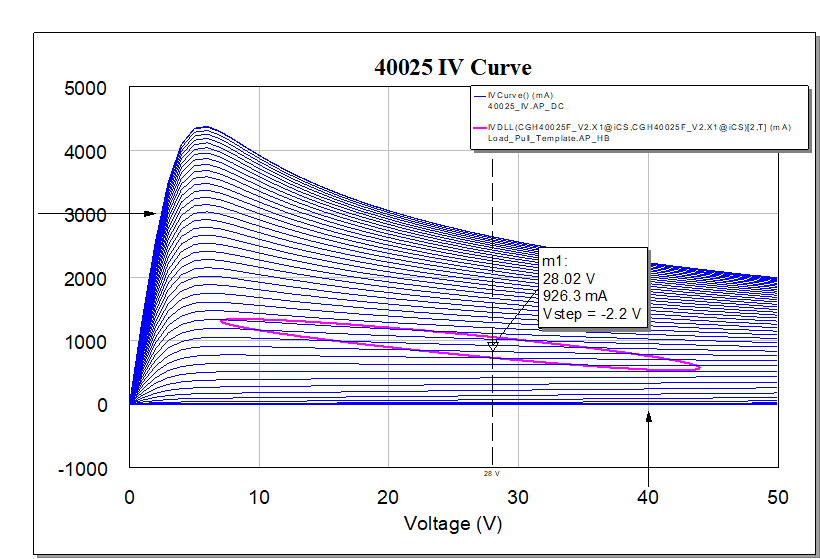

I did an IV curve…

-2.2V gate voltage looks about Class A.

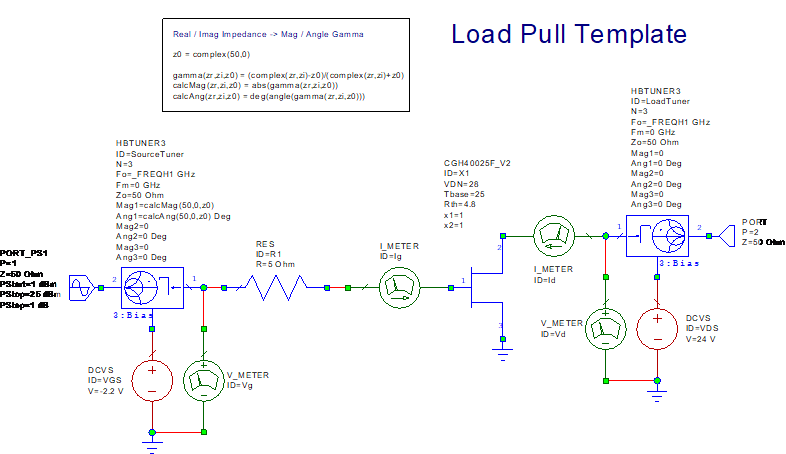

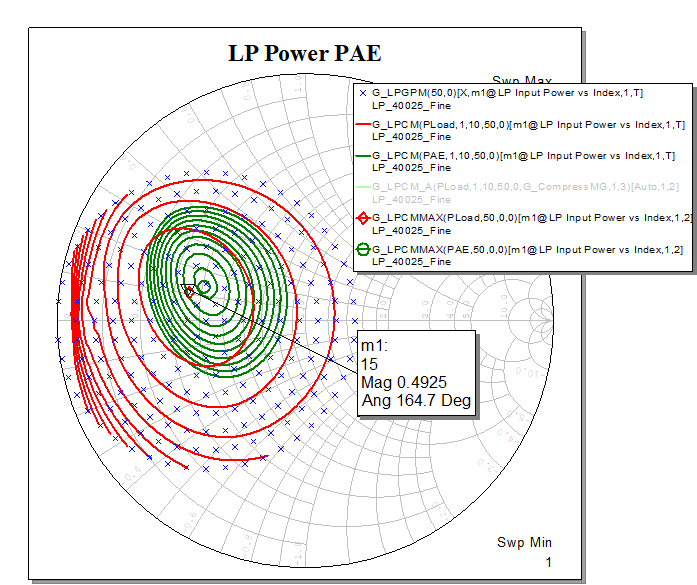

In AWR, I then run a Load Pull and Source Pull to find the impedances I need to match to.

I then would run Network Synthsis that pulls from the LP Tuners to derive a matching network.

Without out the 5 ohm stabilization resistor on the gate, I get error messages from AWR.

Obviously a resistor is not going to be the first device on the input matching network but will likely be somewhere in the matching network…

How do I take into account the stabilization resistor ?

-2.2V gate voltage looks about Class A.

In AWR, I then run a Load Pull and Source Pull to find the impedances I need to match to.

I then would run Network Synthsis that pulls from the LP Tuners to derive a matching network.

Without out the 5 ohm stabilization resistor on the gate, I get error messages from AWR.

Obviously a resistor is not going to be the first device on the input matching network but will likely be somewhere in the matching network…

How do I take into account the stabilization resistor ?