Zena356

Newbie level 3

Hi!

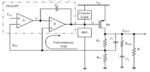

I try to design Low Drop Out regulator (LDO) circuit with load current up to 1.5 A, with Cload about 10µF. and Resr ~ 0.1 - 5 Ω

But I was faced with the problem of stability. With such large output currents, a large output transistor is required, respectively, a large parasitic gate capacitance. Stability is obtained at high currents of 100mA. At low currents, the phase margin is below 30 degrees. Do you know any methods of compensation for this circuit in a wide range of currents?

thank you in advance

I try to design Low Drop Out regulator (LDO) circuit with load current up to 1.5 A, with Cload about 10µF. and Resr ~ 0.1 - 5 Ω

But I was faced with the problem of stability. With such large output currents, a large output transistor is required, respectively, a large parasitic gate capacitance. Stability is obtained at high currents of 100mA. At low currents, the phase margin is below 30 degrees. Do you know any methods of compensation for this circuit in a wide range of currents?

thank you in advance