jkarran

Newbie level 6

I'm having trouble getting all but the very simplest of SPICE simulations to run when I include a comparator....

I'm using some version of (presumably?) SPICE embedded in ALTIUM DESIGNER 6.9, the error I get is 'timestep too small', I suspect it's associated with oddly unstable and unrealistic looking 'high' (full of glitches) output, the low output state seems to be fine, often a few cycles of the input sinusoid simulate before it fails.

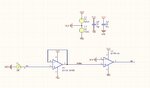

Even a simple very circuit:A small (2V, 50KHz p-p) sinusoid into +IN, -IN to 0V and a decoupled (2x1uF) +-2.5V supply seems to fail. I'd expect a square wave out, *if* it runs I mostly get a mess of high frequency glitches. I'm using or attempting to use various MAXIM models, for example MAX9140, model available from **broken link removed** the model seems to need to be re-named with a .ckt extension (which I've done) and as I'm simply replacing the sim model of another device I've checked and re-assigned the pins to the correct schematic model pins (I'm happy that bit is right). I've tried various devices/models, some with more success than others but none are trouble free and behaving as expected.

MAX9140 boasts rail to rail inputs (I've also tried attenuating the input sinusoid to ~1V p-p so it's nowhere near the supply rails), 3 to 5V single supply operation and a push-pull OP which I've tried OC and driving a 10k load. **broken link removed**

Any and all help appreciated! Cheers,

James

I'm using some version of (presumably?) SPICE embedded in ALTIUM DESIGNER 6.9, the error I get is 'timestep too small', I suspect it's associated with oddly unstable and unrealistic looking 'high' (full of glitches) output, the low output state seems to be fine, often a few cycles of the input sinusoid simulate before it fails.

Even a simple very circuit:A small (2V, 50KHz p-p) sinusoid into +IN, -IN to 0V and a decoupled (2x1uF) +-2.5V supply seems to fail. I'd expect a square wave out, *if* it runs I mostly get a mess of high frequency glitches. I'm using or attempting to use various MAXIM models, for example MAX9140, model available from **broken link removed** the model seems to need to be re-named with a .ckt extension (which I've done) and as I'm simply replacing the sim model of another device I've checked and re-assigned the pins to the correct schematic model pins (I'm happy that bit is right). I've tried various devices/models, some with more success than others but none are trouble free and behaving as expected.

MAX9140 boasts rail to rail inputs (I've also tried attenuating the input sinusoid to ~1V p-p so it's nowhere near the supply rails), 3 to 5V single supply operation and a push-pull OP which I've tried OC and driving a 10k load. **broken link removed**

Any and all help appreciated! Cheers,

James