ku637

Advanced Member level 4

Hello,

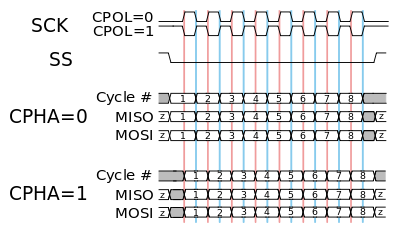

This question may be not correct, but i would like to understand it better the SPI timing diagram. For CPOL=0 CPHA=0 I'm seeing in the following diagram <SPI Timing Diagram> that the MOSI and MISO first bits are shown as set even before the CLK started, right along with the SS signal going down.

Is it really like that i.e. an SPI master will place data (the first bit) on MOSI line even before the CLK started to appear and just when the CS is going down.

Thanks

[ADDED BY MOD]

This question may be not correct, but i would like to understand it better the SPI timing diagram. For CPOL=0 CPHA=0 I'm seeing in the following diagram <SPI Timing Diagram> that the MOSI and MISO first bits are shown as set even before the CLK started, right along with the SS signal going down.

Is it really like that i.e. an SPI master will place data (the first bit) on MOSI line even before the CLK started to appear and just when the CS is going down.

Thanks

[ADDED BY MOD]

Last edited by a moderator: