anantha_09

Member level 4

can any one clearly explain?

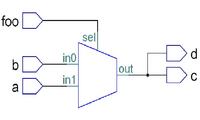

In verilog what is the difference between

c = foo ? a : b;

and

if (foo) c = a; else c = b;

In verilog what is the difference between

c = foo ? a : b;

and

if (foo) c = a; else c = b;