neopisha

Junior Member level 2

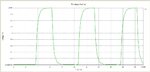

Hi, I am trying to analysis Signal Integrity for a DDR2 SDRAM and OMAPL138 in Altium. There is a problem with signal levels. I've set the Signal Top Value rule to 1.8V for desired nets but in the simulation the default 5V top level signal is injecting. How can I change this value to 1.8V?

I've tried Signal Top Value and Base Value rules and I've edited individual pins but still 5V pulse is injecting!!!!

I've tried Signal Top Value and Base Value rules and I've edited individual pins but still 5V pulse is injecting!!!!