yefj

Advanced Member level 4

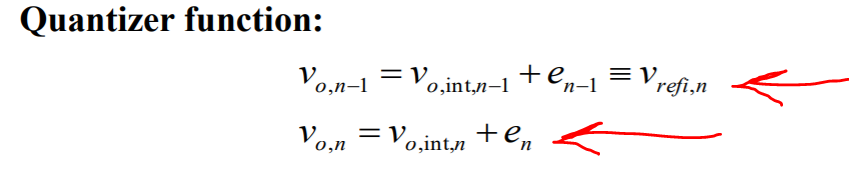

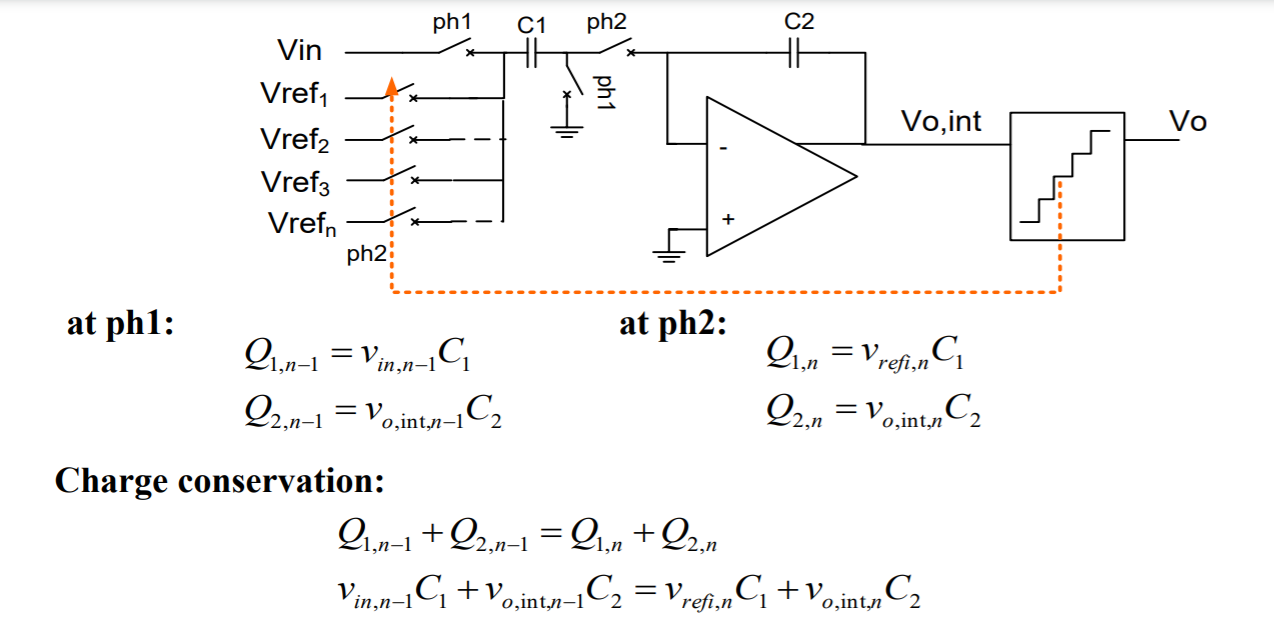

Hello, I amh having trouble to deside the quantizer i am not sure about the expression for Vref and Vo,int regarding the time inside.

I dont know if these two expressions are true:

Why Vo,n=Vo,int+en

e_n is the noise of the quantizer

Vo,int is the signal before the quantizer

if its before the quantizer then they should be N-1 time , Vo,n=Vo,int_n-1+e_n-1

Why its on the same time??I cant see the logic in this.

I dont know if these two expressions are true:

Why Vo,n=Vo,int+en

e_n is the noise of the quantizer

Vo,int is the signal before the quantizer

if its before the quantizer then they should be N-1 time , Vo,n=Vo,int_n-1+e_n-1

Why its on the same time??I cant see the logic in this.

Attachments

Last edited: