skatefast08

Full Member level 3

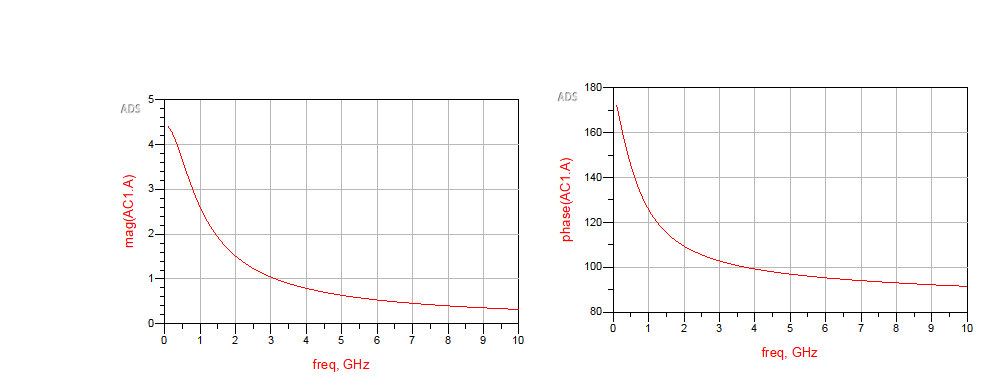

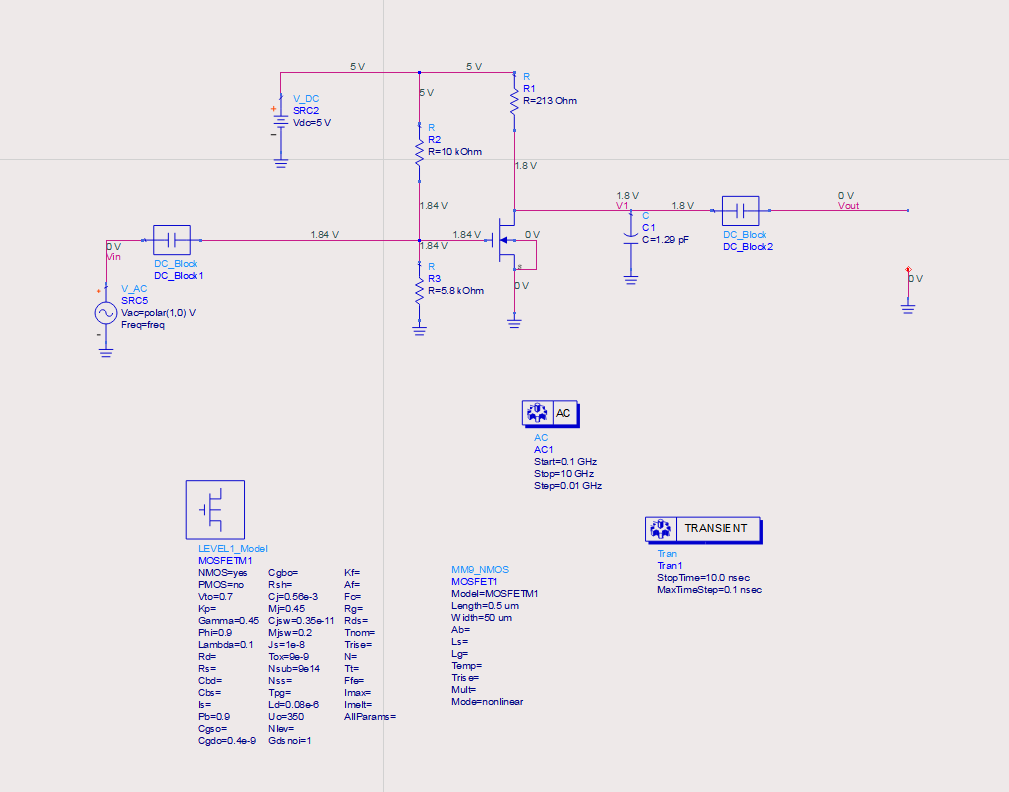

Shouldn't the phase change of this CS amplifier be 180 degrees? If so, then why does my AC phase simulation show every frequency being less than 180 degrees? See details in images. Thanks

Last edited: