celebrevida

Member level 2

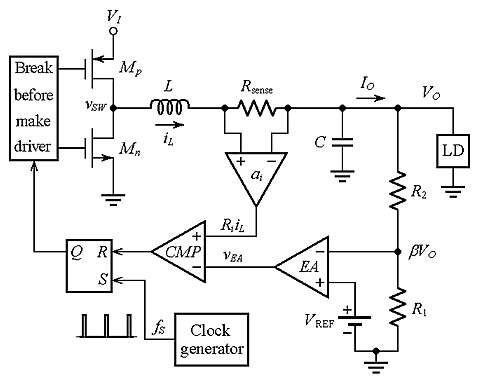

Schematic of a Buck Converter with Peak Current Mode Control

Let's say we have Vi=12V, Vo=5V, Rload=5 (So Iload=1A) at steady state.

Now I bring down Rload->0 (short circuit between Vout and gnd).

Bringing down Vo to zero should increase Vea to a high max value. (EA amp has high gain).

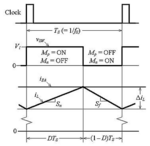

If Vsense=Ri*IL is unchanged, then the two curves should intersect at a later time and CMP resets the FF at a later time.

(Vsense is a ramp and with Vea being higher, it takes longer for the Vsense to reach Vea than before)

This means a larger Duty Cycle D.

But iL actually changed (at least its slope). It used to be (12-5)/L=7/L. But now it is 12/L so IL vs t is steeper.

If Vea never changed, then Vsense intersects Vea at an earlier time and reduces D.

I guess it isn't clear to me whether D ultimately decreased or increased.

Is it knowable or it just depends on particular values?

Okay, at this point, this Dnew (whatever it is) is locked right?

I mean Vea and IL slope are both maxed out and both can't change anymore with Vo shorted to gnd right?

So does this mean that IL(max) is now also maxed out and therefore this circuit is preventing the IL from running away?

Or am I missing something and IL will keep increasing cycle by cycle and blow up anyway somehow?

Thanks for any insight!

Let's say we have Vi=12V, Vo=5V, Rload=5 (So Iload=1A) at steady state.

Now I bring down Rload->0 (short circuit between Vout and gnd).

Bringing down Vo to zero should increase Vea to a high max value. (EA amp has high gain).

If Vsense=Ri*IL is unchanged, then the two curves should intersect at a later time and CMP resets the FF at a later time.

(Vsense is a ramp and with Vea being higher, it takes longer for the Vsense to reach Vea than before)

This means a larger Duty Cycle D.

But iL actually changed (at least its slope). It used to be (12-5)/L=7/L. But now it is 12/L so IL vs t is steeper.

If Vea never changed, then Vsense intersects Vea at an earlier time and reduces D.

I guess it isn't clear to me whether D ultimately decreased or increased.

Is it knowable or it just depends on particular values?

Okay, at this point, this Dnew (whatever it is) is locked right?

I mean Vea and IL slope are both maxed out and both can't change anymore with Vo shorted to gnd right?

So does this mean that IL(max) is now also maxed out and therefore this circuit is preventing the IL from running away?

Or am I missing something and IL will keep increasing cycle by cycle and blow up anyway somehow?

Thanks for any insight!