shahrilmajid

Newbie level 4

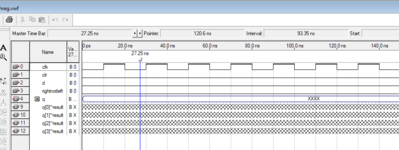

Hi, I was trying to run a shift register in VHDL and was suddenly stuck by this error. Here is my code. I unable to view an output

Code:

library ieee;

use ieee.std_logic_1164.all;

entity shreg is

port( d: in std_logic;

clk : in std_logic;

rightnotleft : in std_logic; -- right 1 into q3 passing to q1

clr: in std_logic; -- right 0 into q3 passing to q1

q: inout std_logic_vector(3 downto 0));

end shreg;

architecture beh of shreg is

begin

process (clk,clr)

begin

if clr ='1' then

q<= "0000";

elsif (clk'event and clk = '1' and rightnotleft ='1') then

q(3) <=d;

q(2 downto 0) <= q (3 downto 1);

elsif (clk 'event and clk = '1') and rightnotleft = '0' then

q(0) <=d;

q(3 downto 1) <= q (2 downto 0);

end if;

end process;

end beh;