antlhem

Member level 1

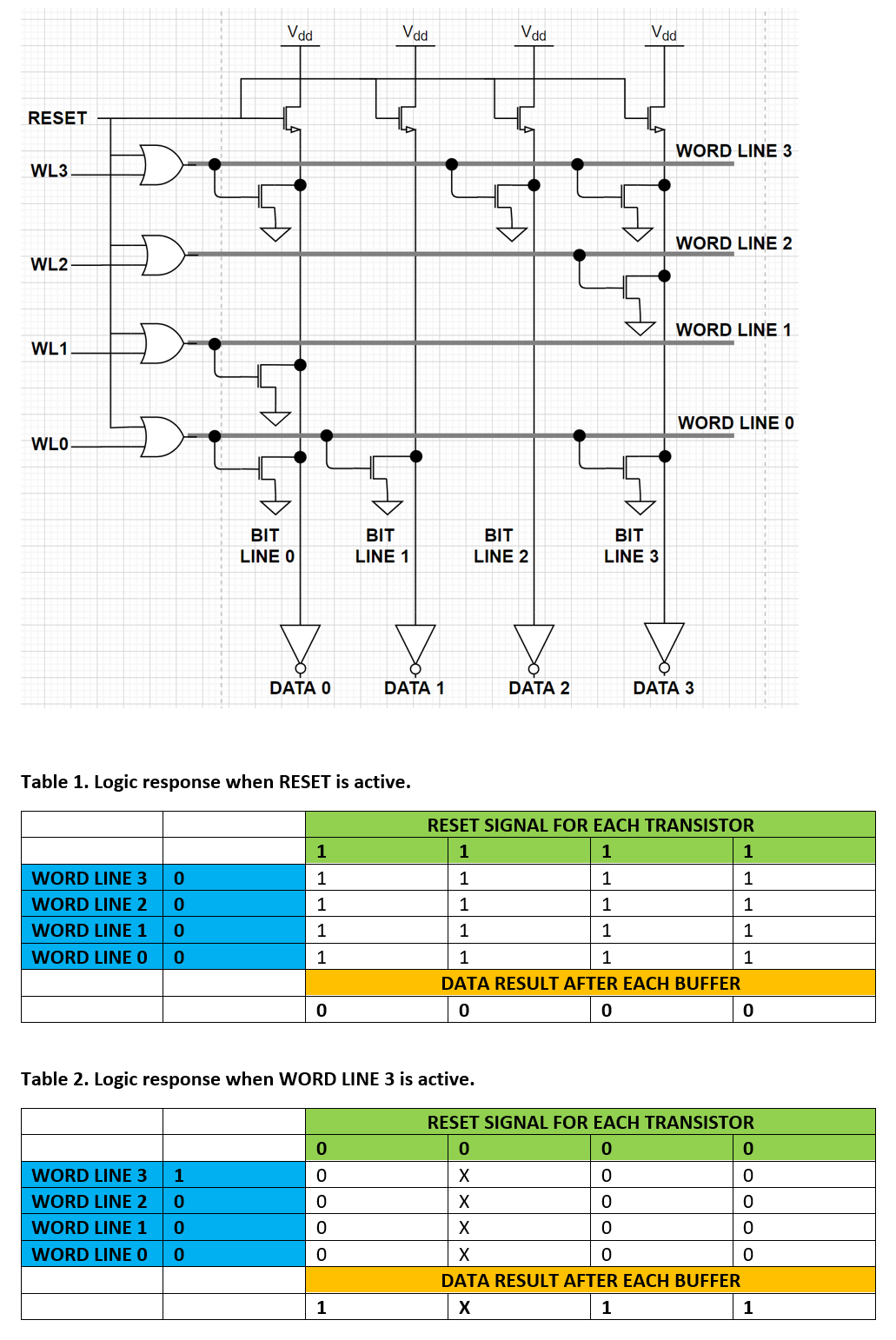

Hi. I am working out the reading data in a simple ROM, my question is, should I expect a don't care in "BIT LINE 1" when "WORD LINE 3" is active?

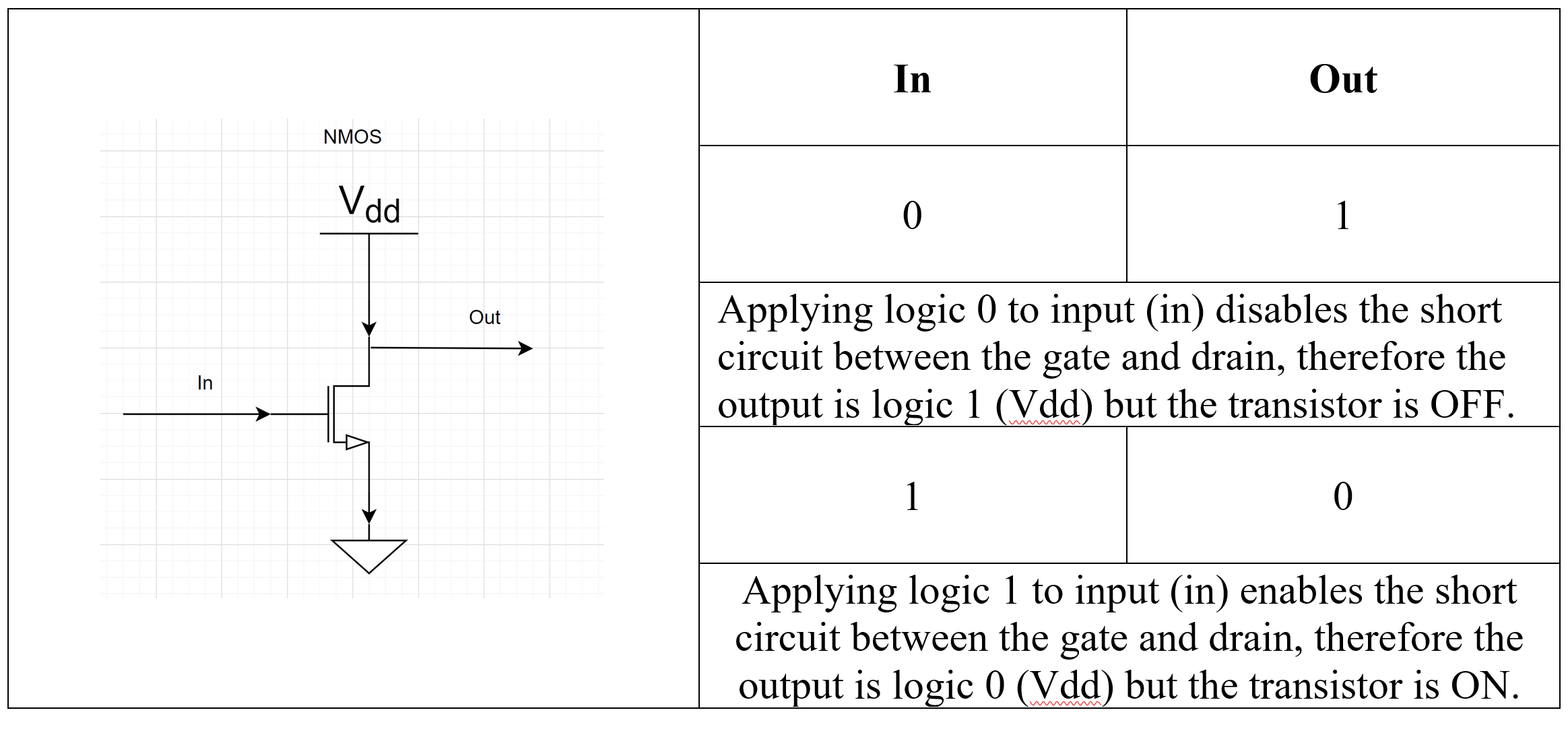

First, I show the basics about NMOS which are the transistors used in this diagram.

Then the small ROM diagram and tables that show the results when WORD LINE 3 is active.

First, I show the basics about NMOS which are the transistors used in this diagram.

Then the small ROM diagram and tables that show the results when WORD LINE 3 is active.