Fractional-N

Full Member level 1

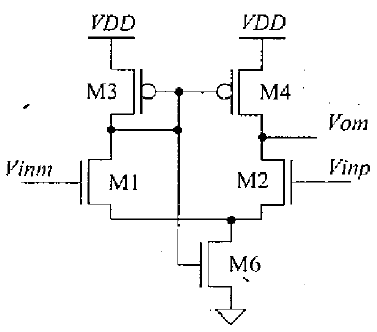

the circuit below is a replica-feedback bias circuit for a differential delay element.

when I simulate the delay chain with this bias circuit, there is a large sensitivity over supply voltage (Vdd); while there shouldn't be. I mean the circuit is not supply insensitive. can anyone help me? does this kind of biasing really work?

thanks

when I simulate the delay chain with this bias circuit, there is a large sensitivity over supply voltage (Vdd); while there shouldn't be. I mean the circuit is not supply insensitive. can anyone help me? does this kind of biasing really work?

thanks