yefj

Advanced Member level 4

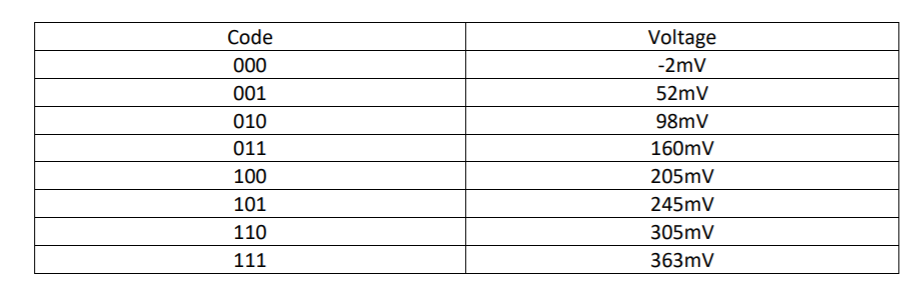

Hello ,i have a 3 bit converter with idial LSB of 50mV ,The following table showing bellow the noon idial logical values.

I need to remove gain and offset errors from the codes bellow.

I read in the internet that one step to remove gain error is to calculate a new LSB by doing an avarage

AVG_LSB=(363-(-2))/(8-1)=52.14V

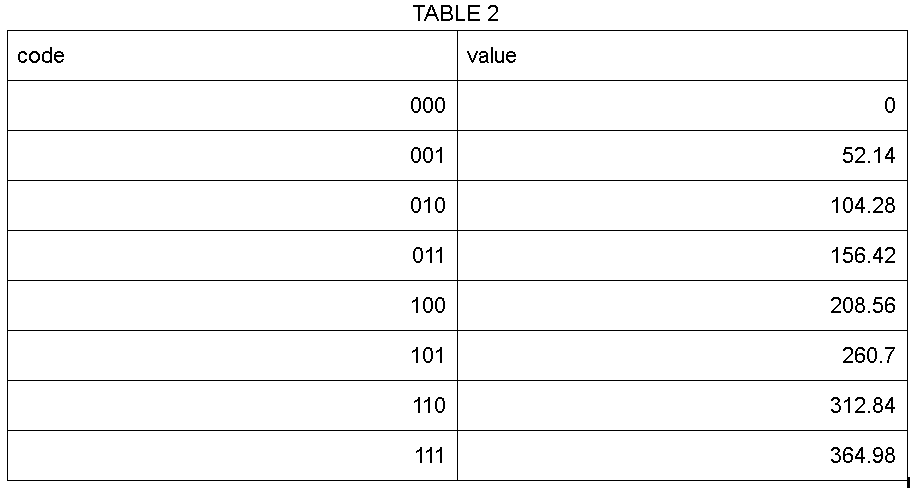

So if i calculate the table using this new LSB(NEW gain) i get table 2 shown bellow.

Did it remove the gain error?if so then Why its called removing gain error??

Thanks.

I need to remove gain and offset errors from the codes bellow.

I read in the internet that one step to remove gain error is to calculate a new LSB by doing an avarage

AVG_LSB=(363-(-2))/(8-1)=52.14V

So if i calculate the table using this new LSB(NEW gain) i get table 2 shown bellow.

Did it remove the gain error?if so then Why its called removing gain error??

Thanks.