keyboardcowboy

Member level 2

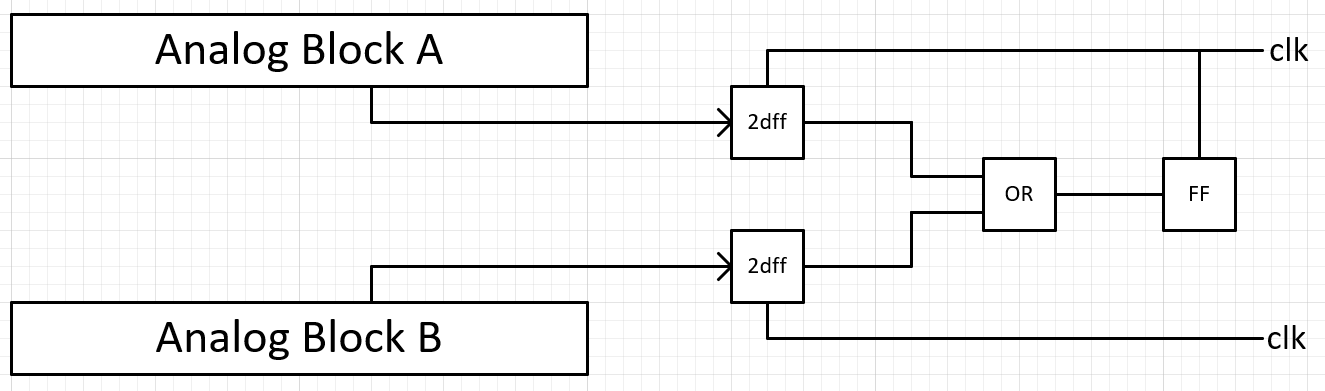

I have 2 similar analog blocks which output a single bit signal. The signal from Block A is not related to the signal from Block B. Before using the signal in my sequential logic, I have synchronized each separately using a 2DFlipFlop synchronizer. CDC checking tools complain that this is a "Re-convergence of synchronizers" problem. How do I get around this?. The analog blocks which generate this signal don't have a clock. It is an async signal. The signal itself is very slow (it rarely changes)