clros

Member level 2

I have a question about static memory.

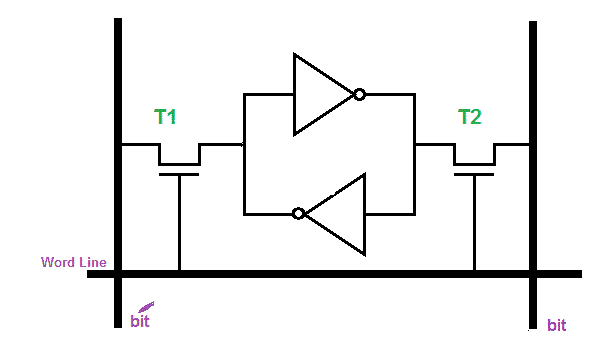

The classic circuit foresees that a static memory cell is formed by two NOT gates as shown in the figure:

My question is: when the pass gates (T1,T2) are off, could the static electricity present in the environment near the chip change the state of the stored bit, inducing a voltage?

The classic circuit foresees that a static memory cell is formed by two NOT gates as shown in the figure:

My question is: when the pass gates (T1,T2) are off, could the static electricity present in the environment near the chip change the state of the stored bit, inducing a voltage?