MagicToad

Newbie

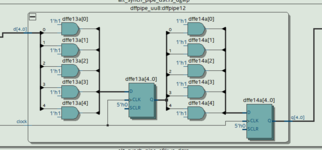

I currently use the quartus, the verison is described in title. And I instantiated an async fifo ip, synthesized it. Then I open the RTL viewer, in a module(its function is to sync the write gray code ptr to read side) I have seen a weird logic combination. In my thought this module should simply have two regs which are used for different clock syncing, but it has each bit of gray_coded ptr through an and gate(the gate's other input is a constant 1) then to a reg then through and gates finally through regs and output to read side. It also did for read to write side.

I did not know why it does that, anyone has any idea?

I did not know why it does that, anyone has any idea?